# Tulsiramji Gaikwad-Patil College of Engineering & Technology, Nagpur Department of Information Technology

<u>Notes</u>

# Academic Session: 2018-2019

Subject: CAO

Semester: IV

# <u>Unit – I</u>

# <u>Syllabus</u>

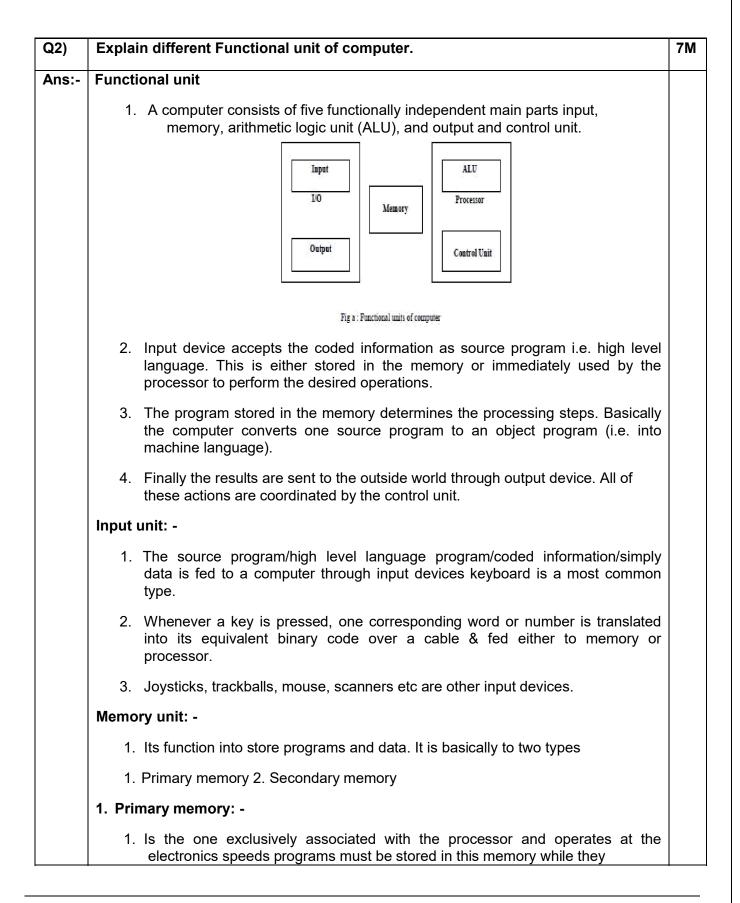

Basic Structure of Computers: Functional Units, Basic Operational Concepts, Bus Structures, Software, Multiprocessors and Multicomputer. Machine Instructions: Memory Locations and Addresses, Memory Operations, Machine program sequencing, addressing modes and encoding of information, Assembly Language, Stacks, Queues and Subroutine.

|       | What is computer? Explain different types of computer.                                                                                                                                                                                                  | 7 <b>M</b> |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Ans:- | Computer types                                                                                                                                                                                                                                          |            |  |  |  |

|       | <ol> <li>A computer can be defined as a fast electronic calculating machine that<br/>accepts the (data) digitized input information process it as per the list of<br/>internally stored instructions and produces the resulting information.</li> </ol> |            |  |  |  |

|       | <ol> <li>List of instructions are called programs &amp; internal storage is called computer<br/>memory.</li> </ol>                                                                                                                                      |            |  |  |  |

|       | The different types of computers are                                                                                                                                                                                                                    |            |  |  |  |

|       | <b>1. Personal computers:</b> - This is the most common type found in homes, schools, Business offices etc., It is the most common type of desk top computers with processing and storage units along with various input and output devices.            |            |  |  |  |

|       | 2. Note book computers: - These are compact and portable versions of PC                                                                                                                                                                                 |            |  |  |  |

|       |                                                                                                                                                                                                                                                         |            |  |  |  |

|       | 3. Work stations: - These have high resolution input/output (I/O) graphics capability, but with same dimensions as that of desktop computer. These are used in engineering applications of interactive design work.                                     |            |  |  |  |

|       | but with same dimensions as that of desktop computer. These are used in engineering                                                                                                                                                                     |            |  |  |  |

|        | are being executed.                                                                                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

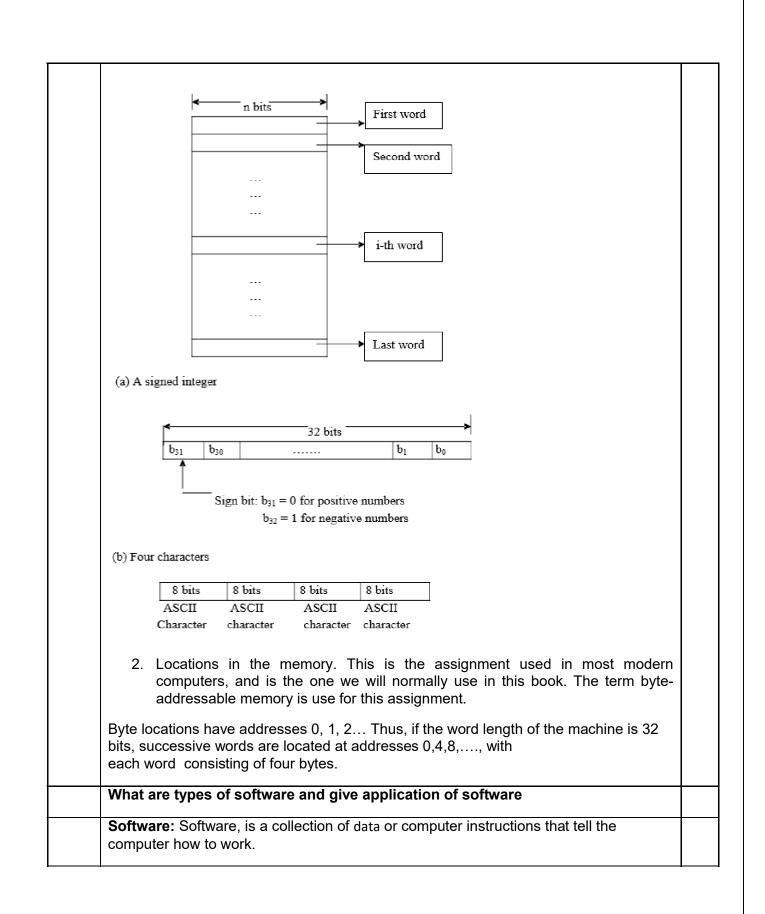

| 2.     | The memory contains a large number of semiconductors storage cells. Each capable of storing one bit of information. These are processed in a group of fixed site called word.                                                                        |

| 3.     | To provide easy access to a word in memory, a distinct address is associated<br>with each word location. Addresses are numbers that identify memory location.                                                                                        |

| 4.     | Number of bits in each word is called word length of the computer. Programs must reside in the memory during execution. Instructions and data can be written into the memory or read out under the control of processor.                             |

| 5.     | Memory in which any location can be reached in a short and fixed amount of time after specifying its address is called random-access memory (RAM).                                                                                                   |

| 6.     | The time required to access one word in called memory access time.<br>Memory which is only readable by the user and contents of which can't be<br>altered is called read only memory (ROM) it contains operating system.                             |

| 7.     | Caches are the small fast RAM units, which are coupled with the processor and are often contained on the same IC chip to achieve high performance. Although primary storage is essential it tends to be expensive.                                   |

| 2 Sec  | ondary memory: -                                                                                                                                                                                                                                     |

| 1.     | Is used where large amounts of data & programs have to be stored, particularly information that is accessed infrequently.                                                                                                                            |

| 2.     | Examples: - Magnetic disks & tapes, optical disks (ie CD-ROM's), floppies etc.,                                                                                                                                                                      |

| Arithr | netic logic unit (ALU):-                                                                                                                                                                                                                             |

| 1.     | Most of the computer operators are executed in ALU of the processor like<br>addition, subtraction, division, multiplication, etc. the operands are brought into<br>the ALU from memory and stored in high speed storage elements called<br>register. |

| 2.     | Then according to the instructions the operation is performed in the required sequence.                                                                                                                                                              |

| 3.     | The control and the ALU are many times faster than other devices connected to a computer system.                                                                                                                                                     |

|        |                                                                                                                                                                                                                                                      |

|       | such as key boards, displays, magnetic and optical disks, sensors and other mechanical controllers.                                                                                                                                                                                                                                     |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | Output unit:-                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|       | <ol> <li>These actually are the counterparts of input unit. Its basic function is to send<br/>the processed results to the outside world.</li> </ol>                                                                                                                                                                                    |  |  |  |  |  |

|       | 2. Examples: - Printer, speakers, monitor etc.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|       | Control unit: - It effectively is the nerve center that sends signals to other units and senses their states. The actual timing signals that govern the transfer of data between input unit, processor, memory and output unit are generated by the control unit.                                                                       |  |  |  |  |  |

| Q3)   | Explain Basic operational concepts of computer.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Ans:- | Basic operational concepts                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

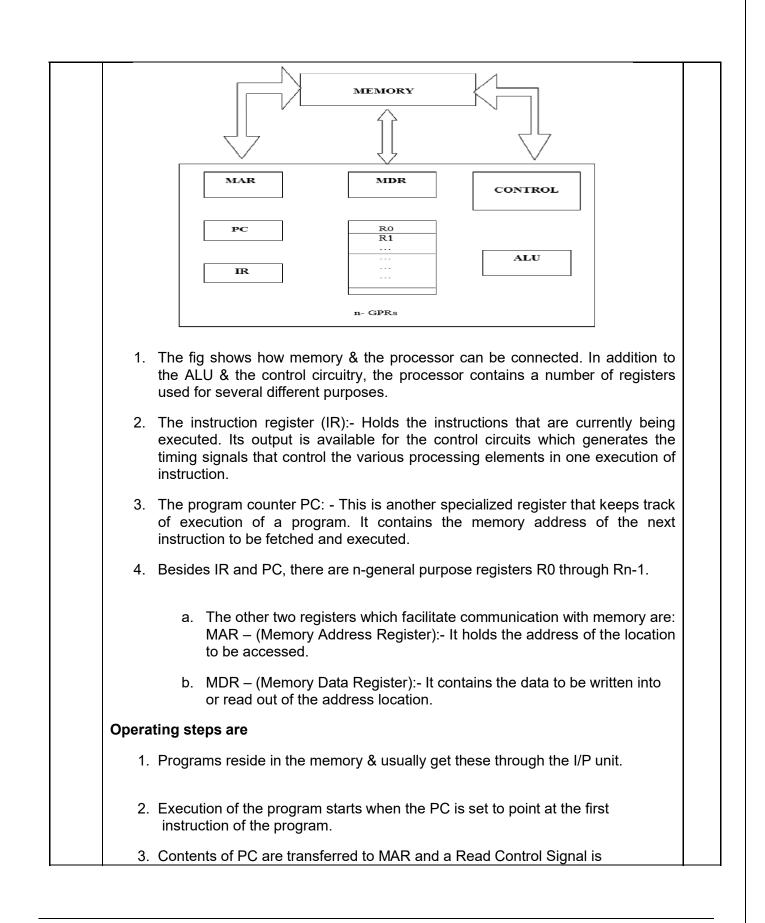

|       | <ol> <li>To perform a given task an appropriate program consisting of a list of<br/>instructions is stored in the memory. Individual instructions are brought from the<br/>memory into the processor, which executes the specified operations. Data to be<br/>stored are also stored in the memory. Examples: - Add LOCA, R0</li> </ol> |  |  |  |  |  |

|       | <ol> <li>This instruction adds the operand at memory location LOCA, to operand in<br/>register R0 &amp; places the sum into register. This instruction requires the<br/>performance of several steps,</li> </ol>                                                                                                                        |  |  |  |  |  |

|       | 1. First the instruction is fetched from the memory into the processor.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|       | 2. The operand at LOCA is fetched and added to the contents of R0                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|       | 3. Finally the resulting sum is stored in the register R0                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | <ol> <li>The preceding ads instruction combines a memory access operation with an<br/>ALU Operations. In some other type of computers, these two types of<br/>operations are performed by separate instructions for performance reasons.</li> </ol>                                                                                     |  |  |  |  |  |

|       | 4. Load LOCA, R1 Add R1, R0 Transfers between the memory and the processor<br>are started by sending the address of the memory location to be accessed to<br>the memory unit and issuing the appropriate control signals. The data are then<br>transferred to or from the memory.                                                       |  |  |  |  |  |

|                | sent to the memory.                                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.             | After the time required to access the memory elapses, the address word is read<br>out of the memory and loaded into the MDR.                                                                                                                                                   |

| 5.             | Now contents of MDR are transferred to the IR & now the instruction is ready to be decoded and executed.                                                                                                                                                                       |

| 6.             | If the instruction involves an operation by the ALU, it is necessary to obtain the required operands.                                                                                                                                                                          |

| 7.             | An operand in the memory is fetched by sending its address to MAR & Initiating a read cycle.                                                                                                                                                                                   |

| 8.             | When the operand has been read from the memory to the MDR, it is transferred from MDR to the ALU.                                                                                                                                                                              |

| 9.             | After one or two such repeated cycles, the ALU can perform the desired operation.                                                                                                                                                                                              |

| 10.            | . If the result of this operation is to be stored in the memory, the result is sent to MDR.                                                                                                                                                                                    |

| 11.            | Address of location where the result is stored is sent to MAR & a write cycle is initiated.                                                                                                                                                                                    |

| 12.            | The contents of PC are incremented so that PC points to the next instruction that is to be executed.                                                                                                                                                                           |

| 1.             | Normal execution of a program may be preempted (temporarily interrupted) if some devices require urgent servicing, to do this one device raises an Interrupt signal.                                                                                                           |

| 2.             | An interrupt is a request signal from an I/O device for service by the processor.<br>The processor provides the requested service by executing an appropriate<br>interrupt service routine.                                                                                    |

| 3.             | The Diversion may change the internal stage of the processor its state must be<br>saved in the memory location before interruption. When the interrupt-routine<br>service is completed the state of the processor is restored so that the<br>interrupted program may continue. |

| Q4) Explain Bu | us structure of computer Ans:-                                                                                                                                                                                                                                                 |

| Bus structure  |                                                                                                                                                                                                                                                                                |

|                | The simplest and most common way of interconnecting various parts of the computer.                                                                                                                                                                                             |

|                | To achieve a reasonable speed of operation, a computer must be organized so that all its units can handle one full word of data at a                                                                                                                                           |

| Q5) | Explain the difference between Multiprocessor & Multicomputer                                                                                                                                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3. Can only be employed where loads can be interrupted or where we have some other supply source                                                                                                                                                                                        |

|     | 2. Failure of bus results in failure of the whole substation                                                                                                                                                                                                                            |

|     | 1. Difficult to do maintenance operations                                                                                                                                                                                                                                               |

|     | Disadvantages:                                                                                                                                                                                                                                                                          |

|     | 2. Simple to operate                                                                                                                                                                                                                                                                    |

|     | 1. Low cost                                                                                                                                                                                                                                                                             |

|     | Advantages:                                                                                                                                                                                                                                                                             |

|     | The instructions from the processor at once are loaded into these buffers and then the complete transfer of data at a fast rate will take place                                                                                                                                         |

|     | 7. All the interconnected devices are not of same speed & time, leads to a bit of<br>a problem. This is solved by using cache registers (ie buffer registers). These<br>buffers are electronic registers of small capacity when compared to the main<br>memory but of comparable speed. |

|     | <ol><li>Multiple bus structure certainly increases the performance but also<br/>increases the cost significantly.</li></ol>                                                                                                                                                             |

|     | Very flexible for attaching peripheral devices                                                                                                                                                                                                                                          |

|     | Low cost                                                                                                                                                                                                                                                                                |

|     | 5. Single bus structure is                                                                                                                                                                                                                                                              |

|     | actively use the bus at any given time. Bus control lines are used to arbitrate multiple requests for use of one bus.                                                                                                                                                                   |

|     | 4. Since the bus can be used for only one transfer at a time, only two units can                                                                                                                                                                                                        |

|     | 3. In addition to the lines that carry the data, the bus must have lines for address and control purpose.                                                                                                                                                                               |

|     | Fig c: Single bus structure                                                                                                                                                                                                                                                             |

|     |                                                                                                                                                                                                                                                                                         |

|     | INPUT MEMORY PROCESSOR OUTPUT                                                                                                                                                                                                                                                           |

|     | given time. A group of lines that serve as a connecting port for several devices is called a bus.                                                                                                                                                                                       |

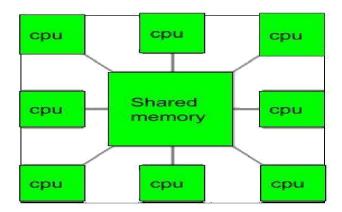

A Multiprocessor is a computer system with two or more central processing units (CPUs) share full access to a common RAM. The main objective of using a multiprocessor is to boost the system's execution speed, with other objectives being fault tolerance and application matching.

There are two types of multiprocessors, one is called shared memory multiprocessor and another is distributed memory multiprocessor. In shared memory multiprocessors, all the CPUs shares the common memory but in a distributed memory multiprocessor, every CPU has its own private memory.

# Applications of Multiprocessor -

- 1. As a uniprocessor, such as single instruction, single data stream (SISD).

- 2. As a multiprocessor, such as single instruction, multiple data stream (SIMD), which is

- 3. usually used for vector processing.

- 4. Multiple series of instructions in a single perspective, such as multiple instruction, single data stream (MISD), which is used for describing hyper-threading or pipelined processors.

- 5. Inside a single system for executing multiple, individual series of instructions in multiple perspectives, such as multiple instruction, multiple data stream (MIMD).

# Benefits of using a Multiprocessor –

- Enhanced performance.

- Multiple applications.

- Multi-tasking inside an application.

- High throughput and responsiveness.

• Hardware sharing among CPUs.

### 2. Multicomputer:

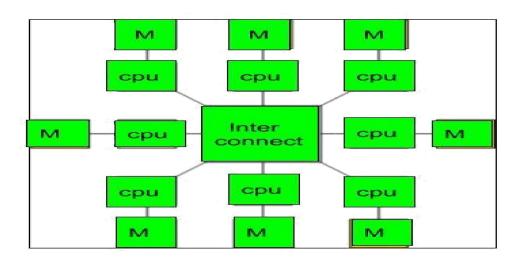

A multicomputer system is a computer system with multiple processors that are connected together to solve a problem. Each processor has its own memory and it is accessible by that particular processor and those processors can communicate with each other via an interconnection network.

As the multicomputer is capable of messages passing between the processors, it is possible to divide the task between the processors to complete the task. Hence, a multicomputer can be used for distributed computing. It is cost effective and easier to build a multicomputer than a multiprocessor.

# Difference between multiprocessor and Multicomputer:

- 1. Multiprocessor is a system with two or more central processing units (CPUs) that is capable of performing multiple tasks where as a multicomputer is a system with multiple processors that are attached via an interconnection network to perform a computation task.

- 2. A multiprocessor system is a single computer that operates with multiple CPUs where as a multicomputer system is a cluster of computers that operate as a singular computer.

- 3. Construction of multicomputer is easier and cost effective than a multiprocessor.

- 4. In multiprocessor system, program tends to be easier where as in multicomputer system, program tends to be more difficult.

- 5. Multiprocessor supports parallel computing, Multicomputer supports distributed computing.

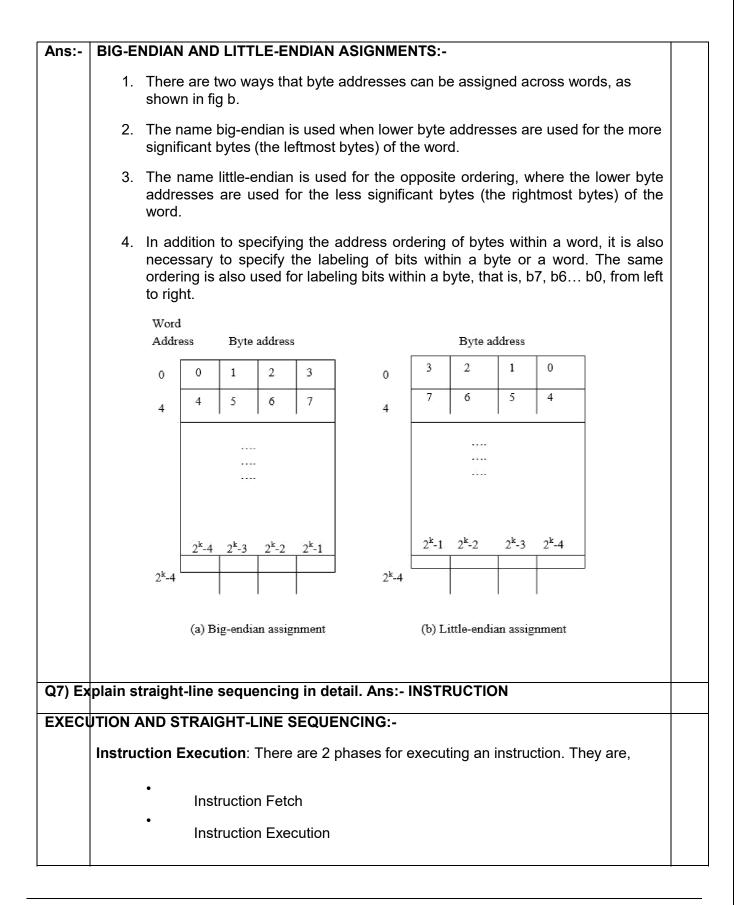

# Q6) Explain the difference between big-endian and little-endian assignments

#### Instruction Fetch:

The instruction is fetched from the memory location whose address is in PC. This is then placed in IR.

#### Instruction Execution:

Instruction in IR is examined and decoded to determine which operation is to be performed.

#### Program execution Steps:

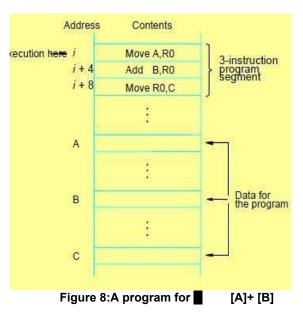

1. The three instructions of the program are in successive word locations, starting at location i. since each instruction is 4 bytes long, the second and third instructions start at addresses i + 4 and i + 8.

- 2. Let us consider how this program is executed. The processor contains a register called the program counter (PC), which holds the address of the instruction to be executed next. To begin executing a program, the address of its first instruction (I in our example) must be placed into the PC.

- 3. Then, the processor control circuits use the information in the PC to fetch and execute instructions, one at a time, in the order of increasing addresses. This is called straight-line sequencing.

- 4. During the execution of each instruction, the PC is incremented by 4 to point to the next instruction. Thus, after the Move instruction at location i + 8 is executed, the PC contains the value i + 12, which is the address of the first instruction of the next program segment.

- 5. Executing a given instruction is a two-phase procedure. In the first phase, called instruction fetch, the instruction is fetched from the memory location whose address is in the PC.

|       | <ol><li>This instruction is placed in the instruction register (IR) in the processor. The<br/>instruction in IR is examined to determine which operation is to be performed.</li></ol>                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | The specified operation is then performed by the processor. This often involves fetching operands from the memory or from processor registers, performing an arithmetic or logic operation, and storing the result in the destination location.                              |

| Q8)   | Explain different Addressing modes with example                                                                                                                                                                                                                              |

| Ans:- | Addressing modes:                                                                                                                                                                                                                                                            |

|       | The term addressing modes refers to the way in which the operand of an instruction is specified. The addressing mode specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually executed                             |

|       | Types of Addressing Modes:                                                                                                                                                                                                                                                   |

|       | <ol> <li>Immediate Addressing Mode –<br/>In immediate addressing mode the source operand is always data. If the data is<br/>8-bit, then the instruction will be of 2 bytes, if the data is of 16-bit then the<br/>instruction will be of 3 bytes.</li> </ol>                 |

|       | <b>Examples:</b><br>MVI B 45 (move the data 45H immediately to register B)<br>LXI H 3050 (load the H-L pair with the operand 3050H immediately)<br>JMP address (jump to the operand address immediately)                                                                     |

|       | <ol> <li>Register Addressing Mode –<br/>In register addressing mode, the data to be operated is available inside the<br/>register(s) and register(s) is(are) operands. Therefore the operation is<br/>performed within various registers of the microprocessor.</li> </ol>   |

|       | <b>Examples:</b><br>MOV A, B (move the contents of register B to register A)<br>ADD B (add contents of registers A and B and store the result in register A INR A<br>(increment the contents of register A by one)                                                           |

|       | <ol> <li>Direct Addressing Mode –<br/>In direct addressing mode, the data to be operated is available inside a memory<br/>location and that memory location is directly specified as an operand. The<br/>operand is directly available in the instruction itself.</li> </ol> |

|       | <b>Examples:</b><br>LDA 2050 (load the contents of memory location into accumulator A)<br>LHLD address (load contents of 16-bit memory location into H-L register pair)<br>IN 35 (read the data from port whose address is 01)                                               |

|       | 4. Register Indirect Addressing Mode –                                                                                                                                                                                                                                       |

a memory location and that memory location is indirectly specified b a register pair. Examples: MOV A, M (move the contents of the memory location pointed by the H-L pair to the accumulator) LDAX B (move contains of B-C register to the accumulator) LXIH 9570 (load immediate the H-L pair with the address of the location 9570) 5. Implied/Implicit Addressing Mode -In implied/implicit addressing mode the operand is hidden and the data to be operated is available in the instruction itself. Examples: CMA (finds and stores the 1's complement of the contains of accumulator A in A) RRC (rotate accumulator A right by one bit) RLC (rotate accumulator A left by one bit) 6. Auto-increment mode: Effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are automatically incremented to point to the next consecutive memory location.(R1)+.Example: Add R1, (R2)+ // OR R1 = R1 + M[R2]R2 = R2 + d7. Auto-decrement mode: Effective address of the operand is the contents of a register specified in the instruction. Before accessing the operand, the contents of this register are automatically decremented to point to the previous consecutive memory location. -(R1)Example: Add R1,-(R2) //OR

IN register indirect addressing mode, the data to be operated is available inside

R2 = R2-d

R1 = R1 + M[R2].

| Name                                                                                                                                                                                                     | Assembler syntax                                                                                                                                                                                                                                       | Addressing function                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Immediate                                                                                                                                                                                                | # Value                                                                                                                                                                                                                                                | Operand = Value                                                                                                                                                                                       |

| Register                                                                                                                                                                                                 | Ri                                                                                                                                                                                                                                                     | EA = Ri                                                                                                                                                                                               |

| Absolute (Direct)                                                                                                                                                                                        | LOC                                                                                                                                                                                                                                                    | EA = LOC                                                                                                                                                                                              |

| Indirect                                                                                                                                                                                                 | (Ri)                                                                                                                                                                                                                                                   | EA = [Ri]                                                                                                                                                                                             |

|                                                                                                                                                                                                          | (LOC)                                                                                                                                                                                                                                                  | EA = [LOC]                                                                                                                                                                                            |

| Index                                                                                                                                                                                                    | X(Ri)                                                                                                                                                                                                                                                  | EA = [Ri] + X                                                                                                                                                                                         |

| Base with index                                                                                                                                                                                          | (Ri, Rj)                                                                                                                                                                                                                                               | EA = [Ri] + [Rj]                                                                                                                                                                                      |

| Base with index                                                                                                                                                                                          | X (Ri, Rj)                                                                                                                                                                                                                                             | EA = [Ri] + [Rj] + X                                                                                                                                                                                  |

| and offset<br>Relative                                                                                                                                                                                   | X(PC)                                                                                                                                                                                                                                                  | EA = [PC] + X                                                                                                                                                                                         |

| Autoincrement                                                                                                                                                                                            |                                                                                                                                                                                                                                                        | EA = [rc] + X<br>EA = [Ri]; Increment Ri                                                                                                                                                              |

| Autodecrement                                                                                                                                                                                            | (Ri)+<br>-(Ri)                                                                                                                                                                                                                                         | EA = [Ri], increment RiDecrement Ri; EA = [Ri]                                                                                                                                                        |

|                                                                                                                                                                                                          | ()                                                                                                                                                                                                                                                     |                                                                                                                                                                                                       |

| EA = effective addre                                                                                                                                                                                     | ess                                                                                                                                                                                                                                                    |                                                                                                                                                                                                       |

| Value = a signed nu                                                                                                                                                                                      | mber                                                                                                                                                                                                                                                   |                                                                                                                                                                                                       |

| ifference betwee<br>Stack:                                                                                                                                                                               | en Stack and Queue                                                                                                                                                                                                                                     | with proper example.                                                                                                                                                                                  |

| Stack:                                                                                                                                                                                                   |                                                                                                                                                                                                                                                        | with proper example.                                                                                                                                                                                  |

| <b>Stack</b> :<br>A stack is a list of                                                                                                                                                                   | f data elements, usua                                                                                                                                                                                                                                  |                                                                                                                                                                                                       |

| <b>Stack</b> :<br>A stack is a list of<br>restriction that ele                                                                                                                                           | f data elements, usua<br>ements can be addeo                                                                                                                                                                                                           | ally words or bytes with the accessing                                                                                                                                                                |

| <b>Stack</b> :<br>A stack is a list of<br>restriction that ele<br>End from which e                                                                                                                       | f data elements, usua<br>ements can be addeo                                                                                                                                                                                                           | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.                                                                      |

| <b>Stack</b> :<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle                                                                                                 | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the                                                                                                                                                         | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.                                                                      |

| Stack:<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle<br>Also known as: P                                                                                     | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the                                                                                                                                                         | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.<br>e stack.<br>Last in first out (LIFO) stack.                       |

| Stack:<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle<br>Also known as: P<br>Push - pla                                                                       | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the<br>Pushdown stack. And                                                                                                                                  | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.<br>e stack.<br>Last in first out (LIFO) stack.<br>he stack.          |

| Stack:<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle<br>Also known as: P<br>D Push - pla                                                                     | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the<br>Pushdown stack. And<br>acing a new item on t                                                                                                         | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.<br>e stack.<br>Last in first out (LIFO) stack.<br>he stack.          |

| Stack:<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle<br>Also known as: P<br>Push - pla<br>Pop - Remov<br>Data stored in the                                  | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the<br>Pushdown stack. And<br>acing a new item on t<br>ving the top item from the s<br>e memory of a compu                                                  | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.<br>e stack.<br>Last in first out (LIFO) stack.<br>he stack.          |

| Stack:<br>A stack is a list of<br>restriction that ele<br>End from which e<br>Other end is calle<br>Also known as: P<br><i>Push</i> - pla<br><i>Pop</i> - Remov<br>Data stored in the<br>Successive elem | f data elements, usua<br>ements can be added<br>elements are added a<br>ed the "bottom" of the<br>Pushdown stack. And<br>acing a new item on t<br>ving the top item from the s<br>e memory of a compu-<br>ents occupy success<br>ents are pushed on to | ally words or bytes with the accessing<br>d or removed at one end of the stack.<br>and removed is called the "top" of the stack.<br>e stack.<br>Last in first out (LIFO) stack.<br>he stack.<br>tack. |

| A gei     | neral purpose register could                                           | serve as a s <sup>t</sup>                                                                                                                                                  | tack pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SI<br>BOT | 2<br>739                                                               | <ul> <li>Byte ad</li> <li>Word le</li> <li>First ele</li> <li>SP point</li> <li>Push op<br/>Subt</li> <li>Pop op<br/>Mov.</li> <li>Add</li> <li>Push w<br/>Mov.</li> </ul> | sor with 65536 bytes of memory.<br>Idressable memory.<br>Ingth is 4 bytes.<br>Idress a bytes.<br>Idress to the stack is at BOTTOM.<br>Its to the element at the top.<br>Idreation can be implemented as:<br>Idreat H4, SP<br>Idreation can be implemented as:<br>Idreat SP<br>Idreat |  |

| б.        | 5535                                                                   |                                                                                                                                                                            | t <u>h autoincrement:</u><br>e (SP)+, A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Sr.No     | STACK                                                                  |                                                                                                                                                                            | QUEUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1         | Objects are inserted and rer<br>the same end.                          | noved at                                                                                                                                                                   | Objects are inserted and removed from different ends.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|           | In stacks only one pointer is<br>points to the top of the stack        |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2         | 3 In stacks, the last inserted ob first to come out.                   |                                                                                                                                                                            | ject is In queues, the object inserted first is first deleted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|           | first to come out.                                                     |                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|           | first to come out.<br>Stacks follow Last In First O<br>order.          |                                                                                                                                                                            | Queues following First In First<br>Out (FIFO) order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |